# **ספריות הטכניון** The Technion Libraries

בית הספר ללימודי מוסמכים ע"ש ארווין וג'ואן ג'ייקובס Irwin and Joan Jacobs Graduate School

> © All rights reserved to the author

This work, in whole or in part, may not be copied (in any media), printed, translated, stored in a retrieval system, transmitted via the internet or other electronic means, except for "fair use" of brief quotations for academic instruction, criticism, or research purposes only. Commercial use of this material is completely prohibited.

> © כל הזכויות שמורות למחבר/ת

אין להעתיק (במדיה כלשהי), להדפיס, לתרגם, לאחסן במאגר מידע, להפיץ באינטרנט, חיבור זה או כל חלק ממנו, למעט "שימוש הוגן" בקטעים קצרים מן החיבור למטרות לימוד, הוראה, ביקורת או מחקר. שימוש מסחרי בחומר הכלול בחיבור זה אסור בהחלט.

# Parallel Additive Fast Fourier Transform Algorithms

Matan Hamilis

© Technion - Israel Institute of Technology, Elyachar Central Library

# Parallel Additive Fast Fourier Transform Algorithms

**Research** Thesis

Submitted in partial fulfillment of the requirements for the degree of Master of Science in Computer Science

### Matan Hamilis

Submitted to the Senate of the Technion — Israel Institute of Technology Tamuz 5776 Haifa July 2016 © Technion - Israel Institute of Technology, Elyachar Central Library

The Research Thesis Was Done Under The Supervision of Prof. Eli Ben-Sasson and Prof. Mark Silberstein, in the Faculty of Computer Science.

Some results in this thesis have been published as articles by the author and research collaborators in conferences and journals during the course of the author's doctoral research period, the most up-to-date versions of which being:

- ICS 16' E. Ben-Sasson, M. Hamilis, M. Silberstein, and E. Tromer, Fast Multiplication in Binary Fields on GPUs via Register Cache, Proceedings of the 30<sup>th</sup> International Conference on Supercomputing, ACM 2016.

- E. Ben-Sasson and I. Ben-Tov and A. Chiesa and A. Gabizon and D. Genkin and M. Hamilis and E. Pergament and M. Riabzev and M. Silberstein and E. Tromer and M. Virza, Computational integrity with a public random string from quasi-linear PCPs, cryptology ePrint Archive, Report 2016/646.

### Acknowledgements

First, I would like to thank my advisors, Eli and Mark, for their infinite patience and for wholeheartedly answering every question I had in any time. For cultivating my curiosity by posing new challenges, for giving me the tools to face these challenges and for pointing out possible research directions along the way.

I would like to thank my family as well, for constantly pushing me to saturate my uncontainable thirst for knowledge, for their inexpressible support and wisdom and for helping me to make one step at a time towards my dreams.

I am thankful for having my friends inside and outside the Technion for being there beside me along the way, for sharing their paths of lives and experiences with mine and for helping me maintaining a balanced, exciting and gladdening life. The importance of your interest in my work is immeasurable and without it, achieving the same results would have been impossible. For those who were listening to me without even understanding what I was talking about just so I would feel comfortable about my achievements and for those who did understand me for their constructive commentary and critique.

Last but not least I would like to thank my students along the years, which undoubtedly I have learned from more than they did from me.

The Generous Financial Help Of The Hilda and Manasche Ben-Shlomo Fellowship And The Technion Is Gratefully Acknowledged. © Technion - Israel Institute of Technology, Elyachar Central Library

# Contents

| List of Figures    |      |                                                                        |                                                                |           |  |  |  |

|--------------------|------|------------------------------------------------------------------------|----------------------------------------------------------------|-----------|--|--|--|

| List of Algorithms |      |                                                                        |                                                                |           |  |  |  |

| Abstract 1         |      |                                                                        |                                                                |           |  |  |  |

| 1                  | Intr | oduct                                                                  | ion                                                            | 3         |  |  |  |

| <b>2</b>           | Pre  | reliminaries                                                           |                                                                |           |  |  |  |

|                    | 2.1  | Finite                                                                 | Extension Fields' Elements and Bases                           | 9         |  |  |  |

|                    |      | 2.1.1                                                                  | Definitions                                                    | 9         |  |  |  |

|                    | 2.2  | Polyne                                                                 | omial Bases                                                    | 10        |  |  |  |

|                    | 2.3  | Norma                                                                  | al Bases                                                       | 11        |  |  |  |

| 3                  | The  | oretic                                                                 | al Discussion                                                  | 13        |  |  |  |

|                    | 3.1  | Fast N                                                                 | Aultiplication in $GF(2^n)$                                    | 13        |  |  |  |

|                    |      | 3.1.1                                                                  | Generalization for Optimized Multiplication in k-Gapped Finite |           |  |  |  |

|                    |      |                                                                        | Fields                                                         | 15        |  |  |  |

|                    |      | 3.1.2                                                                  | Finding a k-Gapped polynomial                                  | 17        |  |  |  |

|                    | 3.2  | 3.2 Generalizing Gao & Mateer's Additive FFT for affine subspaces $18$ |                                                                |           |  |  |  |

|                    |      | 3.2.1                                                                  | Taylor Expansion                                               | 18        |  |  |  |

|                    |      | 3.2.2                                                                  | Additive FFT in Binary Fields Over Affine Subspaces            | 19        |  |  |  |

| 4                  | CP   | U                                                                      |                                                                | 23        |  |  |  |

|                    | 4.1  | Finite                                                                 | Field Arithmetics                                              | 23        |  |  |  |

|                    |      | 4.1.1                                                                  | Element Representation on CPU                                  | 23        |  |  |  |

|                    |      | 4.1.2                                                                  | Finite Field Library API                                       | 23        |  |  |  |

|                    |      | 4.1.3                                                                  | Implementation of multiplication in $GF(2^{64})$               | 24        |  |  |  |

|                    | 4.2  | Parall                                                                 | el FFT and inverse FFT implementation                          | 25        |  |  |  |

| 5                  | GP   |                                                                        | troduction of Register Cache                                   | <b>27</b> |  |  |  |

|                    | 5.1  |                                                                        | uction of GPUs                                                 | 27        |  |  |  |

|                    | 5.2  | 2 Intra-warp register cache                                            |                                                                |           |  |  |  |

|                    |      | 5.2.1                                                                  | Example: 1D k-stencil                                          | 31        |  |  |  |

|                   |                | 5.2.2              | Analysis                                              |   |   |   |  |   |   |   | 32 |

|-------------------|----------------|--------------------|-------------------------------------------------------|---|---|---|--|---|---|---|----|

|                   |                | 5.2.3              | Limitations                                           | • |   | • |  | • | • | • | 34 |

| 6                 | GP             | U - Fi             | nite Field Multiplication                             |   |   |   |  |   |   |   | 37 |

|                   | 6.1            | Seque              | ntial finite field multiplication                     | • |   | • |  |   |   |   | 37 |

|                   |                | 6.1.1              | The CPU CLMUL instruction                             | • |   |   |  |   |   |   | 37 |

|                   |                | 6.1.2              | Sequential polynomial multiplication                  | • |   |   |  |   |   |   | 38 |

|                   | 6.2            | Parall             | el polynomial multiplication                          | • |   | • |  | • |   | • | 39 |

|                   |                | 6.2.1              | Bit slicing                                           | • |   |   |  |   |   |   | 39 |

|                   |                | 6.2.2              | Parallel polynomial multiplication using chunks .     | • |   |   |  |   |   |   | 40 |

|                   | 6.3            | Polyne             | omial multiplication using register cache             | • |   |   |  |   |   |   | 41 |

|                   | 6.4            | Exten              | ding to polynomials of larger degrees $\ldots \ldots$ | • |   | • |  |   |   |   | 43 |

|                   |                | 6.4.1              | Performance comparison of the different designs       |   |   | • |  |   |   |   | 44 |

|                   |                | 6.4.2              | Application to larger fields                          | • |   | • |  |   |   |   | 45 |

|                   |                | 6.4.3              | Using shared memory only for the output               | • |   | • |  | • |   | • | 46 |

| 7                 | Imp            | olemen             | tation of the FFT algorithm on GPU                    |   |   |   |  |   |   |   | 49 |

|                   | 7.1            | Outlin             | ne of the Implementation                              |   |   |   |  |   |   |   | 49 |

|                   | 7.2            | Set U <sub>l</sub> | p for GPU                                             |   |   |   |  |   |   |   | 52 |

|                   | 7.3            | Shift I            | Phase                                                 |   |   |   |  |   |   |   | 52 |

|                   | 7.4            | Taylor             | Expansion Phase                                       |   |   |   |  |   |   |   | 53 |

|                   | 7.5            | Shuffle            | e Phase                                               |   |   |   |  |   |   |   | 55 |

|                   | 7.6            | Linear             | Evaluation Phase                                      |   |   |   |  |   |   |   | 58 |

|                   | 7.7            | Merge              | Phase                                                 | • | • | • |  | • | • | • | 60 |

| 8                 | $\mathbf{Per}$ | formar             | nce                                                   |   |   |   |  |   |   |   | 63 |

|                   | 8.1            | FFT ε              | and Inverse FFT                                       | • |   | • |  |   |   | • | 66 |

| 9                 | Cor            | nclusio            | n and Open Questions                                  |   |   |   |  |   |   |   | 69 |

|                   | 9.1            |                    | usions                                                |   |   |   |  |   |   |   | 69 |

|                   | 9.2            | Some               | open questions                                        | • |   | • |  | • |   |   | 70 |

| Hebrew Abstract i |                |                    |                                                       |   |   |   |  |   |   |   |    |

# List of Figures

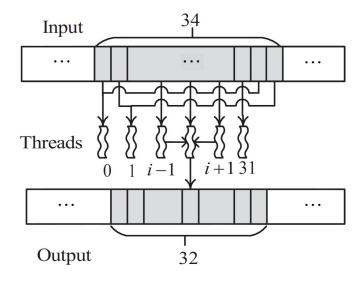

| 5.1 | Input distribution in 1-stencil computation                                                          | 32 |

|-----|------------------------------------------------------------------------------------------------------|----|

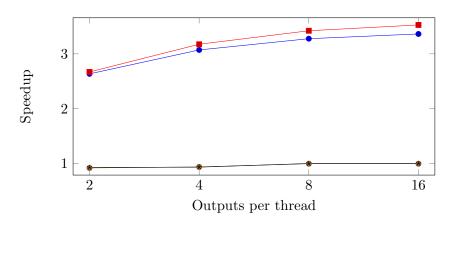

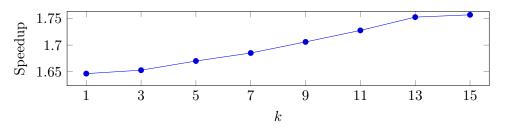

| 5.2 | Speedup obtained from coarsening in the computation of $1 - Stencil$ and                             |    |

|     | 7 - Stencil for register cache and shared memory implementation                                      | 35 |

| 5.3 | Speedup of the shuffle-based k-Stencil implementation over the shared                                |    |

|     | memory-based implementation as a function of $k$                                                     | 35 |

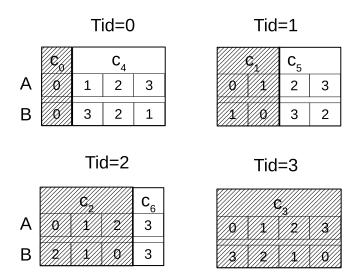

| 6.1 | Illustration of the access pattern of the multiplication algorithm for                               |    |

|     | $GF(2^4)$ with $\mathcal{W} = 4$ . Each frame encloses the indexes of rows in A and B                |    |

|     | accessed for computing the respective rows $c_i$ specified on the top. Tid                           |    |

|     | denotes the thread index in the warp. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 39 |

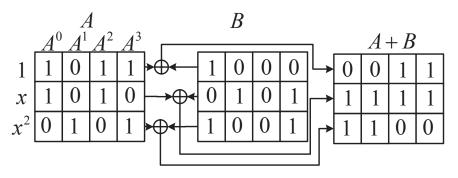

| 6.2 | Polynomial addition in 4-bit chunks. Computing the output chunk                                      |    |

|     | requires 3 bit-wise XORs, each performing 4 concurrent $\oplus$ operations.                          | 40 |

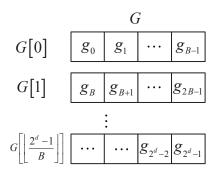

| 7.1 | Storage of Coefficients of Input FFT Polynomial in Chunks                                            | 49 |

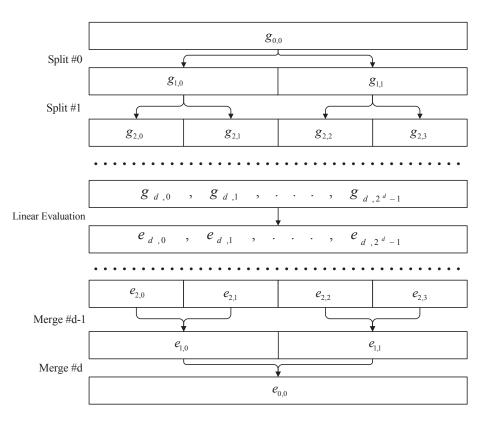

| 7.2 | Outline of the FFT Algorithm                                                                         | 51 |

| 7.3 | Outline of a Single Split Iteration                                                                  | 51 |

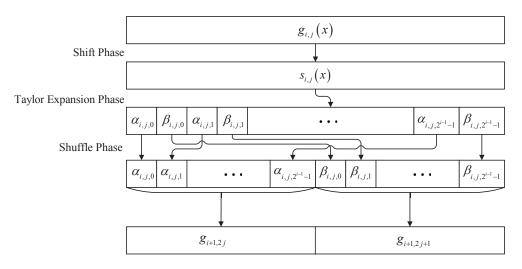

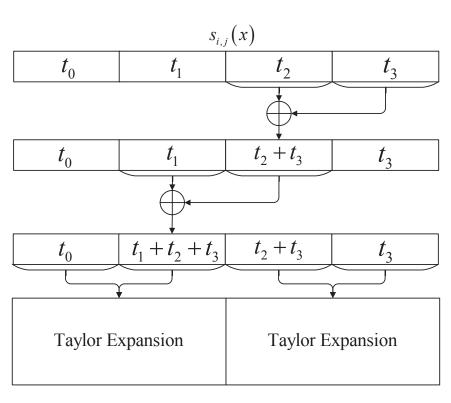

| 7.4 | Outline of the Taylor Expansion Algorithm                                                            | 54 |

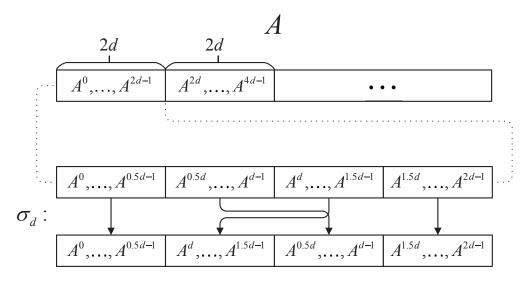

| 7.5 | Applying Permutation $\sigma_d$ on a Chunks' Elements                                                | 57 |

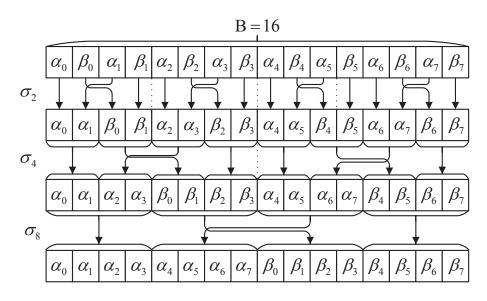

| 7.6 | Applying Permutation $\pi_8$ on a Chunks' Elements                                                   | 58 |

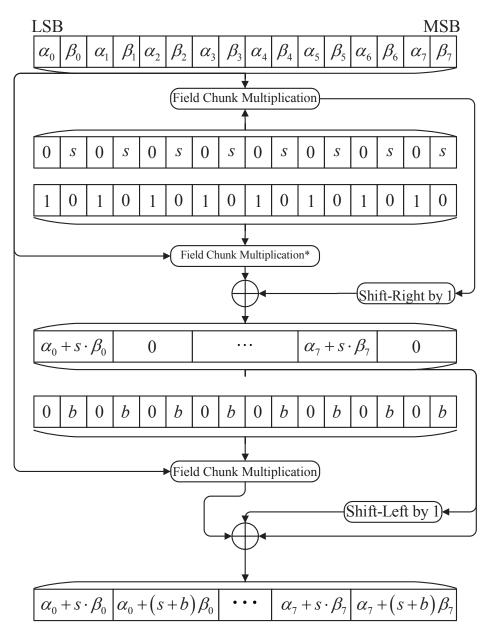

| 7.7 | Linear Evaluation Phase Applied Over a Single Chunk                                                  | 59 |

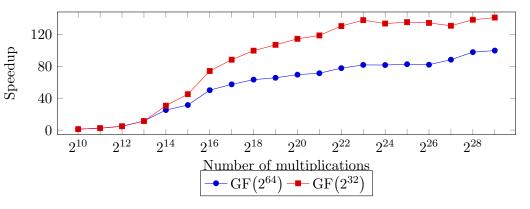

| 8.1 | Speedup of register cache multiplication in $GF(2^{64})$ and $GF(2^{32})$ over                       |    |

|     | NTL                                                                                                  | 64 |

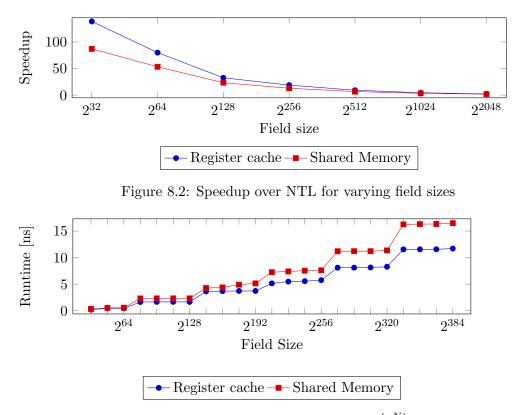

| 8.2 | Speedup over NTL for varying field sizes                                                             | 65 |

| 8.3 | Finite field multiplication performance for $GF(2^N)$ where N is not a                               |    |

|     | power of 2                                                                                           | 65 |

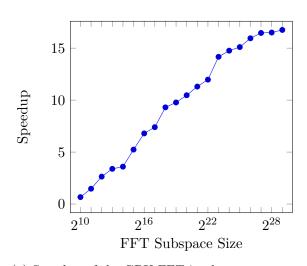

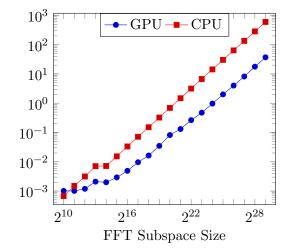

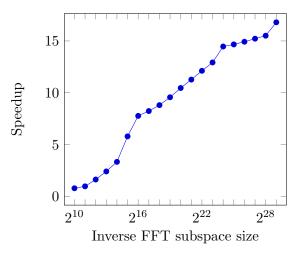

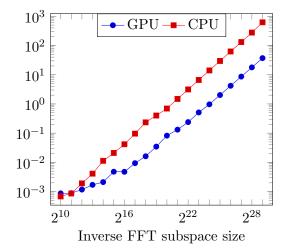

| 8.4 | Comparison of GPU and a single threaded CPU implementation for FFT                                   | 66 |

| 8.5 | Comparison of GPU and a single threaded CPU implementation for                                       |    |

|     | inverse FFT                                                                                          | 66 |

© Technion - Israel Institute of Technology, Elyachar Central Library

# List of Algorithms

| 3.1 | 2-Gapped Multiplication in $GF(2^n)$                | 14 |

|-----|-----------------------------------------------------|----|

| 3.2 | k-Gapped Multiplication in $\operatorname{GF}(p^m)$ | 15 |

| 3.3 | Naïve polynomial multiplication                     | 16 |

| 3.4 | Taylor Expansion at $x^2 - x$                       | 19 |

| 3.5 | Additive FFT of length $n = 2^m$                    | 22 |

| 4.1 | Multiplication in $GF(2^n)$                         | 25 |

| 4.2 | 2-Gapped Multiplication in $GF(2^{64})$ using CLMUL | 25 |

| 6.1 | Multiplication in $GF(2^n)$                         | 38 |

| 6.2 | Naïve polynomial multiplication                     | 38 |

© Technion - Israel Institute of Technology, Elyachar Central Library

# Abstract

Fast Fourier Transforms(FFTs), particularly over finite fields, have a main role in a large set of applications in the fields of signal and image processing, coding and cryptography. The computation of additive FFTs over finite fields is considered as a simpler and more scalable method than multiplicative FFTs due to the additive and recursive structure of finite fields. In this work we present an implementation of an algorithm to compute additive FFTs over finite fields of characteristic two – "binary fields" – to evaluate and interpolate polynomials of high degree over large affine subspaces. While previous works were applied only to linear subspaces, we apply a small modification to an existing algorithm to compute additive FFTs over affine subspaces as well. We present a parallel implementation of this algorithm for the GPU architecture and discuss its performance.

The FFT algorithm relies on an implementation of finite field arithmetics. Binary fields are used in a variety of applications in cryptography and data storage. Multiplication of two finite field elements is a fundamental operation and a well-known computational bottleneck in many of these applications, as they often require multiplication of a large number of elements. In this work we focus on accelerating multiplication in "large" binary fields of sizes greater than  $2^{32}$ . We devise a new parallel algorithm optimized for execution on GPUs. This algorithm makes it possible to multiply large number of finite field elements, and achieves high performance via *bit-slicing* and fine-grained parallelization.

The key to the efficient implementation of the algorithm is a novel performance optimization methodology we call the *register cache*. This methodology speeds up an algorithm that caches its input in shared memory by transforming the code to use per-thread registers instead. We show how to replace shared memory accesses with the **shuffle**() intra-warp communication instruction, thereby significantly reducing or even eliminating shared memory accesses. We thoroughly analyze the register cache approach and characterize its benefits and limitations.

We apply the register cache methodology to the implementation of the binary finite field multiplication algorithm on GPUs. We achieve up to  $138 \times$  speedup for fields of size  $2^{32}$  over the popular, highly optimized Number Theory Library (NTL) [V. 03], which uses the specialized CLMUL CPU instruction, and over  $30 \times$  for larger fields of size below  $2^{256}$ . Our register cache implementation enables up to 50% higher performance compared to the traditional shared-memory based design.

# © Technion - Israel Institute of Technology, Elyachar Central Library

# Chapter 1

# Introduction

### Motivation

Interactive proofs (IP) were introduced to the world by Babai and Moran [L. 88] and by Goldwasser et al. [S. 89]. In an interactive proof, a protocol takes place between two main entities, a computationally-unbounded *Prover* and a computationally-bounded *Verifier*. Along the protocol the prover tries to prove a certain claim to the verifier, while the verifier has to verify the prover's proof using a probabilistic procedure. He can also ask the prover some questions regarding his proof, get the prover's answers and so on. After getting all the information he needs, the verifier can either *accept* or *reject* the proof.

A special kind of IP protocols are called PCP-protocols [L. 90, L. 91, S. 98, AS98] in which the verifier does not read the whole proof given to him by the prover, but only a small and negligible part of it and decides whether to accept or reject the proof according to the part he has read.

A major practical implication of the theorem is the ability to succinctly prove the computational integrity of a program running in time T(n) using a PCP protocol with proof of length **poly** (T(n)) is presented in [L. 90], [L. 91], [Kil92] and [Mic94].

The application motivating this work is to efficiently implement a family of probabilistically checkable proofs (PCP) of quasi-linear length, based on the work of Ben-Sasson and Sudan [E. 08]. This application is envisioned to enable verifiable execution, whereby a client that offloads a computation to untrusted computing resources, e.g., to a cloud system, receives a proof which attests that the results have indeed been produced by the execution of the offloaded computation. This property is also known as *computational integrity* and can be proved using PCPs in which the prover (e.g. the cloud system) proves the computational integrity of a given computation to a verifier (e.g. a client).

Since the prover is computationally unbounded, his role in the PCP protocol can be, theoretically, expensive in terms of computation. And in practice the prover's running time (and space consumption) turns out to be the main bottleneck preventing the system from running in feasible time. The prover executes a program and wishes to prove the computational integrity of its execution to the verifier. To do that it has to encode the execution trace using error correcting codes that possess some interesting properties. It is known that error correcting codes that are based on low-degree polynomials have these properties. Particularly, Ben-Sasson and Sudan in their PCP [E. 08] have used Reed-Solomon codes [I. 60] that are based on univariate polynomials. With other additional restrictions it was required that the Reed-Solomon codes will be evaluated over affine-spaces in finite fields of characteristic-2 or characteristic-q where q - 1 has small prime factors. The execution encoding algorithm is based on the evaluation and interpolation of polynomials over affine subspaces. These can be done efficiently using additive FFTs and inverse FFTs (IFFTs) and the implementation of them in finite fields of characteristic two is the scope of this work.

### **Fast Fourier Transforms**

*Fast Fourier Transforms*(FFTs), particularly over finite fields, have a main role in a large set of applications in the fields of signal and image processing, coding and cryptography [D. 82, R. 02, F. 95, M., Wel67, LRRY78, J. 98b].

The discrete Fast-Fourier-Transform (DFFT) algorithm for finite fields takes as input a polynomial P(x) over a finite field GF  $(p^k)$  and an a set of finite field elements and calculates  $P(\alpha)$  for all  $\alpha$  in that set. The inverse discrete fast Fourier transform (IDFFT) algorithm takes as input a function  $f : S \to \text{GF}(p^k)$  where S is a set of elements from  $\text{GF}(p^k)$  of size n and calculates the interpolation polynomial P(x) over GF  $(p^k)$  of degree n-1 such that for each  $\alpha \in S : P(\alpha) = f(\alpha)$ .

In 1965 the study of the implementation of DFFT algorithms has began by James Cooley and John Tukey who published in their historical paper [J. 65] a full description of an implementation for a DFFT algorithm known to Gauss [Gau66]. This algorithm was a multiplicative-FFT, as evaluating a polynomial over a set that is a multiplicative group and by that utilizing some of the multiplicative properties of that group. In finite fields of low characteristic (e.g.  $GF(2^n)$  there are also additive subgroups over which DFFT algorithm can work. These algorithms, known as additive-DFFTs, evaluate a polynomial over a linear subspace. The computation of additive DFFTs in finite fields over affine subspaces is considered as a simpler and more scalable method than multiplicative DFFTs due to the additive and recursive structure of subspaces in finite fields. In this work we focus on the implementation of additive DFFTs and additive IDFFTs to which we will simply refer as FFTs and IFFTs, as non-discrete FFTs are out of the scope of this work. The first additive FFT / IFFT algorithm for a subspace of size n was the algorithm of Von-Zur-Gather and Gerhard that was published in [J. 03]. This algorithm performs  $O(n \cdot \log^2 n)$  finite field multiplications and additions. In practice, finite field multiplication, is much slower and consumes and might consume a large portion of the running time. Therefore, we wish to find an FFT algorithm that achieves two goals,

- 1. Minimizes the number of finite-field multiplications

- 2. Minimize the time that each multiplication takes.

In this work we present an adaptation of Gao and Matteer's additive FFT and IFFT algorithm to affine subspaces over finite fields of characteristic two [S. 10] with a smaller number of finite field multiplications of  $O(n \cdot \log n)$ , compare to Von-Zur-Gather and Gerhard's algorithm.

We present an implementation of this algorithm to the GPU architectures and evaluate its performance. We implemented a CPU version of the algorithm as well. However, the full details of the implementation of the CPU algorithm is out of the scope of this work and we focus on the GPU implementation.

For completeness, we clarify that the CPU implementation of FFT achieves good running times and can evaluate polynomials of degree  $2^{30}$  over  $2^{30}$  elements in less than 20 minutes in our benchmark using a single thread. However, it scales badly on a high number of CPUs. The reason of this lack of scalability on CPU is left out of the scope of this work.

The GPU implementation gives more than 16x throughput compared to the serial CPU implementation. These implementations' performance heavily relies on the existence of efficient finite field multiplication and the implementation of such on the GPU architecture is the main focus of this work.

### **Finite Fields**

Except for additive FFTs, binary fields have numerous applications in cryptography and data storage. For instance, the Advanced Encryption Standard (AES) [J. 98a] uses GF ( $2^8$ ), as does the error correction scheme used on Compact Discs (CDs) and Digital Versatile Discs (DVDs). Large fields are the basis for distributed storage systems like those used by Google and Amazon, which employ fields of size  $2^{32}$ ,  $2^{64}$  and  $2^{128}$  to ensure secure and reliable storage of data on multiple disks [J. 12]. They are also the basis for the application motivating this work: an efficient implementation of a family of probabilistically checkable proofs (PCP) of quasi-linear length [E. 08]. PCPs require very large binary fields: most of our work focuses on GF ( $2^{32}$ ) and GF ( $2^{64}$ ) but we also support fields of up to GF( $2^{2048}$ ). Because all the applications mentioned above need to perform multiplication of a large number of finite field elements, their performance is dominated by the cost of finite field multiplication, motivating the never-ending quest for more efficient implementations of this fundamental arithmetic operation.

In this work we focus on accelerating finite field multiplication for large binary extension fields of size larger than  $GF(2^{32})$  on GPUs, where field elements are represented using a standard basis (cf. Chapter 2 for definitions). The main computational bottleneck in this case is the multiplication of polynomials over GF(2), that is, polynomials with  $\{0, 1\}$ -coefficients. The challenge posed by polynomial multiplication operations over

GF(2) has led Intel and AMD to add an instruction set extension CLMUL to support it in hardware.

We devise a novel parallel algorithm for multiplication in large binary extension fields on GPUs, which significantly outperforms the dedicated CPU hardware implementation. The algorithm is based on two main ideas: First, we apply *bit-slicing*, enabling a single thread to perform 32 multiplications in parallel. As a result, all the arithmetic operations involved in multiplication are performed on 32 bits together instead of a single bit at a time for single multiplication, therefore matching the width of hardware registers and enabling full ALU utilization. Second, the computation of a single multiplication is further parallelized in a fine-grained manner to eliminate execution divergence among the participating threads. This critical step allows these computations to be mapped to the threads of a single GPU warp, whose threads are executed in lock-step.

We then focus on an implementation of the algorithm on modern NVIDIA GPUs. The key to implementation efficiency is a novel optimization technique that we call the *register cache*. The register cache enables us to use per-thread registers in conjunction with the **shuffle**() intrinsics, that enables intra-warp sharing of register values among threads, to construct a *register-based cache for threads in a single warp*. This cache serves the same purpose as the on-die shared memory, but is much faster thanks to higher bandwidth and reduced synchronization overhead. We propose a general methodology for transforming a traditional algorithm that stores its inputs in shared memory into a potentially more efficient one that uses private per-thread registers to cache the input for the warp's threads. We thoroughly study the benefits and limitations of the register cache approach on the example of a well-known k-Stencil kernel.

Finally, we apply the register cache methodology to optimize the implementation of the finite field multiplication algorithm for  $GF(2^N)$ , where N=32,...,2048. The primary challenge is to scale the efficient single-warp implementation to larger fields while retaining the performance benefits of the register cache methodology. We analyze several design options, and apply an algorithm that uses a low-degree multiplication as a building block for multiplication in larger fields.

We evaluate our implementation across a variety of field and input sizes using NVIDIA Titan-X GPU with 12GB of memory, and compare it to a highly optimized CPU version of a popular Number Theory Library (NTL) [V. 03] running on a single core of Intel<sup>®</sup> Xeon<sup>®</sup> CPU E5-2620 v2 @ 2.10GHz that uses the Intel's CLMUL CPU instruction set extension. Our optimized implementation that uses register cache is up to  $138 \times$  faster than NTL for GF( $2^{32}$ ) when multiplying more than  $2^{25}$  finite field elements. The register cache approach enables us to speed up the original shared memory version by about 50% over all field sizes.

Our contributions in this thesis are as follows:

- 1. A novel algorithm for polynomial multiplication over GF(2) on GPUs,

- 2. A general optimization methodology for using GPU registers as an intra-warp user-managed cache, along with an in depth analysis of this approach and its

application to polynomial multiplication.

- 3. Efficient GPU finite field multiplication that is up to two orders of magnitude faster in fields  $(GF(2^{32}))$  than the CPU implementation that uses the specialized hardware instruction.

- 4. Efficient parallel implementation on CPU and cuda-GPU architectures of the additive FFT and inverse FFT algorithms.

This work is organized as follows. In chapter 2 we give some introductory background information on the theory of finite fields. In chapter 3 we present the problem of finite field multiplication in binary fields and discuss some previous results in that field. We also present the FFT algorithm which we implement in this work. In chapter 4 we briefly present the outlines of our CPU implementation of the FFT algorithm. Chapter 5 introduces the reader to the architecture and computational model of the GPU. In chapter 5.2 we introduce the *Register Cache* methodology to accelerate computation on GPU via caching values in registers. A small use-case example is given in which the benefits of this methodology are present. In chapter 6 we apply the register cache methodology on the multiplication of elements in binary fields. Chapter 7 discusses the implementation of the FFT algorithm in cuda-GPUs. Chapter 8 presents the performance evaluation of our finite field multiplication and FFT algorithms. Main conclusions and open questions for further research are given at chapter 9.

### **Related work**

**2-gapped polynomials** The CPU implementation of NTL [V. 03] for the multiplication in binary fields uses the CLMUL [G. 14] instruction and employs 2-gapped polynomials to replace reduction with multiplications. We apply a similar algorithm in our work.

**SIMD and bit-slicing** The CPU SIMD instructions have been used to perform bitslicing to parallelize  $GF(2^n)$  multiplication [J. 13]. Their implementation, however, is limited to small fields (up to  $GF(2^{32})$ ). The GPU architecture suits SIMD computation and can provide the same functionality as the CPU SIMD instruction set [S. 11]. The proposed implementation is, however, also limited to small fields (e.g  $GF(2^{16})$ ). Our implementation applies to larger fields.

Finite field multiplication on GPUs The previous works [J. 13, S. 11] are limited to fields of size smaller than  $2^{32}$ . Particularly, Plank [J. 13] shows a CPU implementation that deals with computing a product of multiple elements by a single scalar, using scalar-dependent pre-computed lookup tables. Our work focuses on multiplying many *pairs of arbitrary elements*, therefore the lookup table approach is inapplicable.

Cohen et al. [A. 10] describes an implementation of finite field multiplication in specific binary fields. The performance reported in their paper is 3-orders of magnitude slower than the performance reported in our work, and their implementation would benefit from bit slicing, register cache and reduced synchronization techniques presented here.

An implementation of finite field multiplication on GPUs over GF(q) for some specific large NIST primes q is discussed in [K. 12]. Our implementation, however, is optimized for binary fields in a scalable fashion to achieve a generic implementation for a large variety of field sizes.

**Register-based optimizations** The benefits of reusing data in registers on GPUs to boost performance are well known. Volkov and Demmel [V. ] present GPU implementations of LU decomposition and SGEMM.

Enfedaque et al. [P. 15] show how to implement the DWT (discrete wavelet transform) of an image of varying sizes where each warp calculates a different part of the output. They also show that shuffle-based communication achieves better results when the data each warp fetches from global memory is reused more times, as also confirmed by our results (cf. Section 5.2).

Davidson and Owens [A. 11] suggest a method called *register packing* to reduce shared memory traffic in GPU when dealing with a downsweep patterned computation, by performing some parts of the computation in registers.

Catanzaro et al. [B. 14] show a shuffle-based implementation for SIMD architectures, including the GPU. They discuss the benefits of the instruction for reducing sharedmemory bandwidth and show the relation to the Array of Structs – Struct of Arrays transforms.

nVIDIA's Kepler Tuning Guide [nVi15] stresses the benefits of registers over shared memory in terms of latency and capacity. The **shuffle** instruction is suggested as an alternative for the use of shared memory in some cases.

We leverage the lessons learned in the previous work, and take one additional step by suggesting a register cache design methodology for reducing shared memory accesses to the input data. We demonstrate the application of this methodology on a challenging case of finite field multiplication in binary fields, and show that it achieves significant performance benefits.

# Chapter 2

# Preliminaries

This chapter briefly reminds the basic elements of polynomial rings and Galois fields that are necessary to our implementation of additive FFTs. For a thorough introduction to Galois fields see, e.g., [R. 97a].

The structure of this chapter is a follows; First a general definition to finite fields is given, then we discuss two of the most common representations for finite field elements, the *Polynomial Bases* and *Normal Bases*.

In the following chapters all references to finite field elements assume these are represented using a polynomial basis. The definition of a normal basis, being yet another popular representation for finite fields elements, is given here for completeness. We do not discuss the implementation of finite field multiplication represented using normal bases in this work.

### 2.1 Finite Extension Fields' Elements and Bases<sup>1</sup>

### 2.1.1 Definitions

A finite field or Galois field is a field with a finite number of elements. It is known that the number of elements in a finite field can only be a power of a prime number. Let pbe a prime and q be a power of p, we denote by  $GF(q^n)$  or  $F_{q^n}$  the Galois-Field with  $q^n$  elements, which can be viewed as an extension field over  $F_q$  of order n. Therefore  $F_{q^n}$  can interpreted as a vector space of dimension n over  $F_q$ . Let  $\alpha_0, \alpha_1, \ldots, \alpha_{n-1}$  be nlinearly independent elements in  $F_{q^n}$  over  $F_q$ . Any element  $e \in F_{q^n}$  can be represented as  $e = \sum_{i=0}^{n-1} a_i \cdot \alpha_i$  where  $a_i \in F_q$ . We use the notation  $e = (a_0, a_1, \ldots, a_{n-1})$  to state the  $e = \sum_{i=0}^{n-1} a_i \cdot \alpha_i$ .

Let  $a = (a_0, a_1, \ldots, a_{n-1}), b = (b_0, b_1, \ldots, b_{n-1})$  be two elements in  $F_{q^n}$ . The addition of a and b is defined as  $a + b = (a_0 + b_0, a_1 + b_1, \ldots, a_{n-1} + b_{n-1})$  which is a simple component-wise addition of the entries of a and b over  $F_q$ . However, multiplication tends to be not only more complicated but also more time consuming. We now give

<sup>&</sup>lt;sup>1</sup>Definitions are based on [Gao93]

a general definition for the multiplication operation over finite extension fields using *multiplication tables*.

Denote by  $T^0, T^1, \ldots, T^{n-1}$  be *n* matrices of size  $n \times n$  over  $F_q$  s.t.

$$\alpha_i \alpha_j = \sum_{k=0}^{n-1} T_{ij}^k \alpha_k$$

So,  $T_{ij}^k$  is the coefficient of  $\alpha_k$  in the product of  $\alpha_i$  with  $\alpha_j$ . Given three elements  $a, b, c \in F_{q^n}$  such that  $c = a \cdot b$  and  $c = (c_0, c_1, \ldots, c_{n-1})$  the component  $c_k$  in the multiplication  $a \cdot b$  is defined as  $c_k = a \cdot T^k \cdot b$ .

### 2.2 Polynomial Bases

The ring of polynomials Given a prime p GF(p) is the field with p elements  $(0, 1, \ldots, p-1)$ , with addition  $(\oplus)$  and multiplication  $(\odot)$  performed modulo p.

GF (2) is a field with two elements (0,1), with addition  $(\oplus)$  and multiplication  $(\odot)$  performed modulo 2. A polynomial over GF(2) is an expression of the form  $A(x) := \sum_{i=0}^{d} a_i x^i$ , where  $a_i \in GF(2)$  and x is a formal variable; henceforth we simply call A(x) a polynomial because all finite field elements in this work are represented as polynomials over GF (2). The degree of A, denoted deg(A), is the largest index i such that  $a_i \neq 0$ . Addition and multiplication of polynomials (also called ring addition and multiplication) are defined in the natural way, i.e., for  $B(x) = \sum_{i=0}^{m} b_i x^i$  with  $m \ge d$ we have  $A(x) \oplus B(x) = \sum_{i=0}^{m} (a_i \oplus b_i) x^i$  and  $A(x) \odot B(x) = \sum_{j=0}^{d+m} x^j \cdot \bigoplus_{i=0}^{j} a_i \odot b_{j-i}$ . The set of polynomials, augmented with the operations of addition and multiplication defined above, forms the ring of polynomials over GF(2), denoted GF (2) [x]. Later, we reduce the problem of efficient multiplication in the field GF (2<sup>n</sup>) to the problem of multiplying polynomials in the ring GF (2) [x].

The standard representation of a binary field The most common way to represent GF (2<sup>n</sup>), also used here, is via a standard basis, as described next. A polynomial  $r(x) \in \text{GF}(2)[x]$  of degree n is called *irreducible* if there is no pair of polynomials  $g(x), f(x) \in \text{GF}(2)[x]$  such that  $r(x) = g(x) \odot f(x)$  and deg(g), deg(f) < n. Many irreducible polynomials exist for every degree n. (Later, a special class of irreducible polynomials will be used to speed up multiplication.) Having fixed an irreducible r(x), for every pair A, B of polynomials of degree < n, there exists a unique polynomial C of degree < n such that r(x) divides  $A(x) \odot B(x) \oplus C(x)$  in the ring GF (2) [x]; i.e., there exists C'(x) such that  $A(x) \odot B(x) \oplus C(x) = r(x) \odot C'(x)$ . Denote the transformation that maps the pair of polynomials (A(x), B(x)) to the polynomial C(x)by  $\otimes_r$ , where r is used to emphasize that this transformation depends on the irreducible polynomial r(x). The set of polynomials of degree < n, along with ring addition  $\oplus$  and multiplication  $\otimes_r$  defined above, is a *standard basis* representation<sup>2</sup> of GF (2<sup>*n*</sup>). When the irreducible polynomial *h* is clear from context, we shall often drop it and denote GF (2<sup>*n*</sup>) multiplication simply by  $\otimes$ .

**Example of multiplication in standard representation** In this example we show the field multiplication of two elements in GF (2<sup>4</sup>), using the standard representation induced by the irreducible degree-4 polynomial  $r(x) := x^4 + x + 1$ . Consider the two elements  $A(x) = x + x^3$  and  $B(x) = 1 + x^2$ , represented in the standard basis by a := (1010), b := (0101). To compute the 4-bit string  $c = a \otimes_r b$  we work as follows:

- Compute the product C'(x) of the two polynomials A(x), B(x) in the ring GF (2) [x], namely,  $C'(x) := A(x) \odot B(x) = (x + x^3) \odot (1 + x^2) = x + 2x^3 + x^5$  (middle term canceled because we work modulo 2).

- Compute the remainder C(x) of the division of C'(x) by r(x); in our example  $C(x) = x^2$  and one can verify that  $\deg(C) < 4$  and  $r(x) \odot x = C'(x) \oplus C(x)$ , as defined above.

Thus,  $a \otimes_r b = c$  where c := (0100).

Field multiplication reduces to ring multiplication The previous definitions and example show two main points that we exploit next. First, when multiplying two elements in the standard representation induced by r(x), it suffices to (i) multiply polynomials in the ring GF (2) [x] and then (ii) compute the remainder modulo r(x). Second, the structure of r(x) may influence the complexity of computing field multiplication.

### 2.3 Normal Bases

Given an element  $\alpha \in F_{q^n}$  a normal basis for over  $F_q$  has the special form of  $\alpha, \alpha^q, \ldots, \alpha^{q^{n-1}}$ , let us denote by  $\alpha_i$  the element  $\alpha^{q^i}$ . Notice the fact that  $\alpha_i^{q^j} = \alpha_{i+j}$ . Therefore, given an element  $a = a_0, a_1, \ldots, a_{n-1}$  in  $F_{q^n}$  note that  $a^q = (a_{n-1}, a_0, a_1, \ldots, a_{n-2})$  so taking an element to the power of q is computationally simple as a right cyclic shift of the vector once and taking an element to the power of  $q^k$  is doing a cyclic shift by k places.

In our case, for q = 2, it is important not only that squaring can be executed in a fast manner for itself, because fast squaring affects the time needed for exponentiation using the repeated squaring and multiplication method, which by itself can make the inversion over the field much faster.

Additional important advantage is derived from the following observation,  $\alpha_i \cdot \alpha_j = (\alpha \cdot \alpha_{j-i})^i$  (assuming  $j \ge i$ ). So the  $k^{th}$  coefficient of  $\alpha_i \cdot \alpha_j$  is the  $k^{th}$  coefficient of  $(\alpha \cdot \alpha_{j-i})^i$  which is the k-i coefficient of  $\alpha \cdot \alpha_{j-i}$ . Therefore for all i, j, k where k, j > i it holds that  $T_{ij}^k = T_{0,j-i}^{k-i}$ , by taking k = i. So in fact we only need a multiplication

<sup>&</sup>lt;sup>2</sup>The term "basis" refers to the algebraic fact that the *n* elements  $1, x, x^2, \ldots, x^{n-1}$  are linearly independent over GF (2), i.e., they form a basis for GF (2<sup>*n*</sup>) over GF (2); cf. [R. 97a] for more information.

table for  $\alpha \cdot \alpha_i$  for all  $0 \leq i < n$  and by this reducing by one dimension the size of multiplication tables, saving more space. Luckily, it was proved that there is a normal basis for any finite Galois extension of fields (The normal basis theorem), conjectured by Eisenstein in 1850 [Eis50] and first proved by Hensel in 1888 [Hen88].

In conclusion, only one multiplication table would suffice, notice that the time needed to multiply two elements depends on the number of non-zero entries in the table which will be called the *complexity of the base* and will be denoted by c(N) where N is the normal basis of the field. So, we will be interested in bases with low complexities. An important theorem proved by Mullin et al. [R. 89] states that for each normal basis N of  $F_{q^n}$  over  $F_q$ ,  $c(N) \ge 2n - 1$ , bases with this complexity will be called *optimal normal bases*. Optimal normal bases don't exist for all n for q = 2, but according to [Gao93] for 27 values of n where  $2 \le n \le 64$  for which there exist a normal basis in  $F_{2^n}$  over  $F_2$ .

## Chapter 3

# **Theoretical Discussion**

### **3.1** Fast Multiplication in $GF(2^n)$

Finite field multiplication is generally far more time consuming than addition, both in terms of bit operations and in terms of machine cycles, when turning into finite field software implementation. This particularly holds for the fields we are interested in, finite fields of characteristic 2.

Multiplication speed in  $GF(2^n)$  is tightly connected to the field representation (addition is XOR under any basis for  $GF(2^n)$  over GF(2)). Two of the most common representations are, as stated in chapter 2,

- 1. Standard Basis: Elements are polynomials in GF(2)[X] and multiplication is carried out modulo an irreducible polynomial of degree n over GF(2)[X].

- 2. Normal Basis: Elements are the Frobenius automorphisms of a basic element  $\alpha$  and multiplication is defined by a matrix. See [Gao93] for additional details.

We work under the standard basis. To speed up multiplication we choose a special kind of irreducible polynomial, called a 2-gapped polynomial. We show that multiplication in  $GF(2^n)$  can be reduced to one multiplication of polynomials of degree n-1 and two multiplications of polynomials of degree  $\frac{n}{2}$  over the ring GF(2)[X] and 2n additions in GF(2). Let us first introduce the notion and importance of k - Gapped polynomials in  $GF(2^n)$  field for k = 2, as described in algorithm 3.1.

**Definition 3.1.1.** An irreducible polynomial  $r(x) = \sum a_i x^i$  of degree d is **k-Gapped** if it can be written as  $r(x) = x^d - r_1(x)$  where deg $(r_1(x)) \leq d/k$

Denote by  $h_i(x)$  the value of h(x) calculated on step *i* in algorithm 3.1

**Lemma 3.1.2.**  $h_1(x) \equiv h_2(x) \mod r(x)$

### Algorithm 3.1 2-Gapped Multiplication in $GF(2^n)$ Input: • a(x), b(x) of degree at most n - 1 in $\mathbb{F}_2[X]$ . • $r(x) = x^n - r_1(x)$ , 2-Gapped polynomial in $\mathbb{F}_2[X]$ of degree n. Output: $h(x) = (a(x) * b(x)) \mod r(x)$ 1: $h(x) \leftarrow a(x) * b(x)$ 2: $h(x) \leftarrow h_0^{3n/2-1}(x) \oplus h_{3n/2}^{2n-1}(x) \odot r_1(x) * x^{n/2}$ 3: $h(x) \leftarrow h_0^{n-1}(x) \oplus h_n^{3n/2}(x) \odot r_1(x)$

4: return h(x)

Proof.

$$\begin{aligned} a(x) \cdot b(x) &= h_1(x) \\ &= h_1^0(x) + x^{3n/2} \cdot h_1^1(x) & \deg\left(h_1^i(x)\right) \le n/2 - 1 \\ &\equiv h_1^0(x) + r_1(x) \cdot h_1^1(x) \cdot x^{n/2} \mod r(x) & x^n \equiv r_1(x) \mod r(x) \\ &= h_2(x) \mod r(x) \end{aligned}$$

Lemma 3.1.3. deg  $(h_2(x)) \leq \frac{3n}{2} - 1$

Proof.

$$\deg(h_2(x)) = \max\left(\deg(h_1^0(x)), \deg(x^{n/2}) + \deg(h_1^1(x)) + \deg(r_1(x))\right)$$

$$\leq \max(n-1, n/2 + n/2 - 1 + n/2)$$

$$= 3n/2 - 1$$

**Lemma 3.1.4.**  $h_2(x) \equiv h_3(x) \mod r(x)$

Proof.

$$h_{2}(x) = h_{2}^{0}(x) + x^{n} \cdot h_{2}^{1}(x) \qquad \qquad \deg \left(h_{2}^{0}(x)\right) \le n - 1 \qquad \deg \left(h_{2}^{1}(x)\right) \le n/2 - 1$$

$$\equiv h_{2}^{0}(x) + r_{1}(x) \cdot h_{2}^{1}(x) \mod r(x) \qquad \qquad x^{n} \equiv r_{1}(x) \mod r(x)$$

$$= h_{3}(x) \mod r(x)$$

**Lemma 3.1.5.** deg  $(h_3(x)) \le n - 1$

Proof.

$$\deg(h_3(x)) = \max\left(\deg\left(h_2^0(x)\right), \deg\left(h_2^1(x)\right) + \deg\left(r_1(x)\right)\right)$$

$$\leq \max(n-1, n/2 - 1 + n/2)$$

$$= n/2 - 1$$

Algorithm 3.2 k-Gapped Multiplication in  $GF(p^m)$ Input: • a(x), b(x) of degree at most m - 1 in  $\mathbb{F}_p[x]$ . •  $r(x) = x^m - r_1(x)$ , k-Gapped polynomial in  $\mathbb{F}_p[x]$  of degree m. Output:  $h(x) = (a(x) \cdot b(x)) \mod r(x)$ 1:  $\ell \leftarrow m/k$ 2:  $h(x) \leftarrow a(x) \odot b(x)$ 3: for i = k - 1 down to 0 do 4:  $t \leftarrow m + \ell \cdot i$ 5:  $h(x) \leftarrow h_0^{t-1}(x) \oplus h_t^{t+\ell-1}(x) \odot r_1(x) \odot x^{t-m}$ 6: return h(x)

**Lemma 3.1.6.**  $h_3(x) = (a(x) \cdot b(x) \mod r(x))$

*Proof.* From lemma 3.1.2 and lemma 3.1.4 we get  $h_3(x) \equiv a(x) \cdot b(x) \mod r(x)$ . From lemma 3.1.5 we get that deg  $(h_3(x)) \leq n-1$  so the equality holds.

Algorithm 3.1 minimizes number of polynomial multiplications, can be adapted to multiplication in our field of interest,  $GF(2^{64})$ .

### 3.1.1 Generalization for Optimized Multiplication in k-Gapped Finite Fields

In algorithm 3.2 we also present an extension to finite field multiplication in general k - Gapped fields  $GF(p^m)$ .

Let us denote by A(n) and M(n) as the numbers of additions and multiplications in GF(p) that performed when multiplying to polynomials of degree at most n over the ring GF(p)[X].

Theorem 3.1. Algorithm 3.2 performs,

- $2m + A(m-1) + k \cdot A\left(\frac{m}{k}\right)$  additions in  $GF(p^k)$ .

- $M(m-1) + k \cdot M\left(\frac{m}{k}\right)$  multiplications in  $GF(p^k)$

*Proof.* We will count separately the number of operations within polynomials multiplications and out of them.

- The number of additions in  $\operatorname{GF}(p^k)$  which are not part of polynomial multiplications is at most 2m. In each iteration we add the polynomial  $h_t^{t+\ell-1}(x) \odot r_1(x) \odot x^{t-m}$  which has at most  $\frac{2m}{k}$  non-zero coefficients, which are the topmost coefficients, while others will be zero. This addition requires  $\frac{2m}{k}$  additions. Over k iterations there will be 2m additions in total.

- There are no multiplications in GF(p) except for those which are part of polynomial multiplications.

| Algorithm 3.3 Naïve polynomial multiplication      |

|----------------------------------------------------|

| Input:                                             |

| a(x), b(x) of degree at most $n-1$ .               |

| <b>Output:</b> $c(x) = a(x) \odot b(x)$            |

| 1: for $i = 0,, n - 1$ do                          |

| 2: $c_i \leftarrow 0$                              |

| 3: <b>for</b> $j = 0,, i$ <b>do</b>                |

| 4: $c_i \leftarrow c_i \oplus a_j \odot b_{i-j}$   |

| 5: <b>for</b> $i = n,, 2n - 2$ <b>do</b>           |

| 6: $c_i \leftarrow 0$                              |

| 7: <b>for</b> $j = i,, 2n - 2$ <b>do</b>           |

| 8: $c_i \leftarrow a_{n-1+i-j} \odot b_{j-n+1}$    |

| 9: return $c(x) = \sum_{i=0}^{2n-2} c_i \cdot x^i$ |

|                                                    |

• Let us denote by A(n) and M(n) the number of additions and multiplications in GF(p) needed to multiply two polynomials of degree n over the ring GF(p) [X] respectively. Our algorithm first multiplies two polynomials of degree at most m-1 in and then multiplies k times polynomials of degree  $\frac{m}{k}$ , all over the ring GF(p) [X]. This takes  $M(m-1)+k \cdot M\left(\frac{m}{k}\right)$  multiplications and  $A(m-1)+k \cdot A\left(\frac{m}{k}\right)$  additions in  $GF(p^k)$

Notice that the number of multiplications and additions depends on the algorithm that is used to multiply polynomials. The complexity of polynomial multiplication has been extensively studied. The number of bit operations of the naïve algorithm (see Algorithm 3.3) is  $O(n^2)$ . More sophisticated algorithms by Karatsuba [KO63] and by Schonhage and Strassen [SS71, D. 91] are asymptotically faster, requiring  $O(n^{\log_2 3})$  and  $O(n \log n \log \log n)$  bit operations, respectively.

In this work we use the naïve Algorithm 3.3 because it is fastest for polynomials of degrees below 1000 [M. 05] and its simplicity makes it a prime starting point for study.

**Lemma 3.1.7** (Correctness). Algorithm 3.2 outputs  $(a(x) \cdot b(x)) \mod r(x)$ .

*Proof.* Denote by  $h_j(x)$  the value of h(x) as computed after the iteration in which i = j and  $h_k(x)$  will be h(x) before the loop. So  $h_k(x) = a(x) \cdot b(x)$ . We will prove by induction on j that  $h_j(x) \equiv (a(x) \cdot b(x)) \mod r(x)$  and that the degree of  $h_j(x)$  is at most  $m + j \cdot \ell - 1$ .

In the base case, j = k, and  $h_k(x) = a(x) \cdot b(x)$  so its' degree is at most 2m and the claim obviously holds.

Assume the for some n we know that the claim holds, now we shall prove it for n-1. Denote by t the value of variable t in this iteration where  $t = m + \ell \cdot (n-1)$ . According to step 5 of the algorithm  $h_{n-1}(x) = (h_n)_0^{t-1}(x) + (h_n)_t^{t+\ell-1}(x) \cdot r_1(x) \cdot x^{t-m}$  so,

$$\deg(h_{n-1}(x)) = \deg\left((h_n)_0^{t-1}(x) + (h_n)_t^{t+\ell-1}(x) \cdot r_1(x) \cdot x^{t-m}\right)$$

= max  $\left(\deg\left((h_n)_0^{t-1}(x)\right), \deg\left((h_n)_t^{t+\ell-1}(x) \cdot r_1(x) \cdot x^{t-m}\right)\right)$

= max  $(t-1, \ell-1+\ell+t-m)$

Since  $k \ge 2$  then  $\ell = m/k \le m/2$  so.

$$\deg (h_{n-1}(x)) \le \max (t - 1, 2 \cdot m/2 + t - m)$$

= max (t - 1, t - 1)

= t - 1

= m + l \cdot (n - 1) - 1.

Now we shall prove by induction that  $h_i(x) \equiv h_k(x) \mod r(x)$ . The base case is obvious for k. Assume that  $h_n(x) \equiv h_k(x) \mod r(x)$ , since deg  $(h_n(x)) \leq m + \ell \cdot (n) - 1$  then, it can be written as  $(h_n)_t^{t+\ell-1}(x) \cdot r_1(x) \cdot x^{t-m}$

$$h_{n-1}(x) = (h_n)_0^{t-1}(x) + (h_n)_t^{t+\ell-1}(x) \cdot r_1(x) \cdot x^{t-m}$$

$$\equiv (h_n)_0^{t-1}(x) + (h_n)_t^{t+\ell-1}(x) \cdot x^m \cdot x^{t-m} \mod r(x)$$

$$= (h_n)_0^{t-1}(x) + (h_n)_t^{t+\ell-1}(x) \cdot x^t$$

$$= h_n(x)$$

So we return  $h_0(x)$  of degree at most m-1 the equivalent to  $h_k(x) = a(x) \cdot b(x)$ modulo r(x), which proves the correctness of the algorithm.  $\Box$

### 3.1.2 Finding a k-Gapped polynomial

According to Lidl and Niederreiter [R. 97b] the probability that a randomly chosen polynomial is irreducible is roughly 1/n. In a paper published by HP [G. 98] it was mentioned that in binary extension fields, it should be quite probable (i.e. probability is bigger than a constant) to find k - Gapped pentanomials for k s.t.  $\binom{k}{3} \approx n$ , they also present a list of k - Gapped pentanomials that satisfy this equality for any practical n. They also raise an open question whether do irreducible binary pentanomials exist of degree n that are  $\Omega(\sqrt[3]{n^2})$  gapped.

Notice that multiplying any polynomial of degree m by a quadrinomial or pentanomial can be done in O(m), so under the assumptions presented in [G. 98], this is a modular reduction in the polynomial ring GF (2) [X] with linear time complexity.

### 3.2 Generalizing Gao & Mateer's Additive FFT for affine subspaces

The Additive FFT algorithm introduced by Gao and Matteer [S. 10], when applied to binary fields, evaluates a  $2^n - 1$  degree polynomial over a subspace of dimension n for general n in a finite field of characteristic two. It was the first algorithm that broke the  $\Omega(n \cdot \log^2(n))$  multiplications barrier, with only  $O(n \cdot \log(n))$  base field multiplications. See [Mat08] for previous FFT algorithms with the same runtime that were suited only for subspaces with dimensions which is a power of two.

We present a variation of that algorithm that fits affine subspaces as well. For the sake of completeness, we will describe the whole algorithm, relying on formulations and notations used by Gao and Mateer in their paper mentioned above.

### 3.2.1 Taylor Expansion

The additive FFT algorithm computes at some points the generalized Taylor expansion of polynomials at  $(x^2 - x)$ . A more general definition can be found in [J. 03] and [S. 10].

Given a polynomial  $f(x) \in \mathbb{F}[x]$  of degree strictly smaller than  $n = 2^{k+2}$  where  $\mathbb{F}$  is a finite field of characteristic 2, the taylor expansion algorithm of f at  $(x^2 - x)$  finds  $m = \frac{n}{2}$  linear functions  $h_0(x), h_1(x), ..., h_{m-1}(x) \in \mathbb{F}[x]$ , such that,

$$f(x) = h_0(x) + h_1(x) \cdot (x^2 - x) + \dots + h_{m-1} \cdot (x^2 - x)^{m-1}$$

We will denote this expansion as

$$T(f,n) = (h_0, ..., h_{m-1})$$

To compute the Taylor expansion, we first write f(x) as  $f(x) = f_0(x) + x^{2^{k+1}} \left( f_1(x) + x^{2^k} f_2(x) \right)$ where

- deg  $f_0 < 2^{k+1}$

- deg  $f_1 < 2^k$

- deg  $f_2 < 2^k$

$\mathbb F$  is a finite field of characteristic two, therefore,

$$x^{2^{k+1}} = (x^2 - x)^{2^k} + x^{2^k}$$

thus

$$f(x) = f_0(x) + x^{2^k} \left( f_1(x) + f_2(x) \right) + (x^2 - x)^{2^k} \left( f_1(x) + f_2(x) + x^{2^k} f_2(x) \right)$$

### **Algorithm 3.4** Taylor Expansion at $x^2 - x$

Input: (f, n) where  $n \ge 1$  and  $f(x) \in \mathbb{F}[x]$  of degree < n. Output: T(f, n), the taylor expansion of f(x) at  $x^2 - x$ . 1: if  $n \le 2$  then 2: return f(x)3: Find k such that  $2^{k+1} < n \le 2^{k+2}$ . 4: Divide f(x) into three parts as  $f(x) = f_0(x) + x^{2^k+1} \left( f_1(x) + x^{2^k} f_2(x) \right)$ 5: Set  $h \leftarrow f_1 + f_2$ ,  $g_0 \leftarrow f_0 + x^{2^k} h$ ,  $g_1 \leftarrow h + x^{2^k} f_2$ . 6:  $V_1 \leftarrow T(g_0, n/2)$ 7:  $V_2 \leftarrow T(g_1, n/2)$ 8: return  $(V_1, V_2)$

Let  $h(x) = f_1(x) + f_2(x)$ ,  $g_0(x) = f_0(x) + x^{2^k}h(x)$ ,  $g_1(x) = h(x) + x^{2^k}f_2(x)$ . Then,

$$f(x) = g_0(x) + g_1(x)(x^2 - x)^{2^k}$$

Due to the degrees of  $f_0, f_1, f_2$  we know that

$$\deg q_0, q_1 < 2^{k+1}$$

Therefore,

$$T(f,n) = \left(T(\left(g_0, 2^{k+1}\right)), T\left(g_1, 2^{k+1}\right)\right)$$

The time complexity of the algorithm, as described in [S. 10] is,

$$\begin{aligned}

\leq n \cdot \lceil \log_2(n/t) \rceil, & \text{for any } n \\

= \frac{1}{2}n \lceil \log_2(n/t) \rceil, & \text{when } n/t \text{ is a power of two}

\end{aligned}$$

(3.1)

A full description of the algorithm can be found in algorithm 3.4.

### 3.2.2 Additive FFT in Binary Fields Over Affine Subspaces

In this section we will conform with the notations of Gao and Mateer and extend their algorithm presented in [S. 10] to calculate additive FFTs over any affine subspace and not only over subspaces.

Our additive FFT algorithm works over a finite field  $\mathbb{F}$  of characteristic 2. It gets as input a polynomial  $f(x) \in \mathbb{F}[x]$ , a basis of a subspace  $\langle \beta_1, \ldots, \beta_m \rangle$  of dimension m, where  $\beta_1, \ldots, \beta_m$  are linearly independent over GF(2), it also gets as input an affine shift  $s_B$ .

Let us define an ordering of the elements of *B*. Given a number  $0 \le i < 2^m$  with binary representation

$$i = a_1 + a_2 \cdot 2 + \dots + a_m \cdot 2^{m-1} = (a_1, a_2, \dots, a_m)_2$$

Where each  $a_j$  is either 0 or 1. The  $i^{th}$  element of affine subspace B is

$$B[i] = s + a_1\beta_1 + a_2\beta_2 + \dots + a_m\beta_m.$$

The algorithm's output is the evaluation of f(x) over all elements in the affine subspace  $B = s_B + \langle \beta_1, ..., \beta_m \rangle$ , and will be denoted as,

$$FFT(f, m, B) = (f(B[0]), f(B[1]), \cdots, f(B[2^m - 1]))$$

The algorithm is recursive, we show how to reduce a problem of size n > 2 to two problems of size  $k = n/2 = 2^{m-1}$ . Let

$$\begin{aligned} \gamma_i &= \beta_i \cdot \beta_m^{-1}, \quad 1 \le i \le m - 1\\ s_G &= s_B \cdot \beta_m^{-1} \end{aligned}$$

and

$$G = s_G + \langle \gamma_1, ..., \gamma_m \rangle \tag{3.2}$$

Let  $g(x) = f(\beta_m x)$ . Evaluating f(x) over B is equivalent to the evaluation of g(x) over  $G \cup (G+1)$ . So we wish to calculate FFT(g, G) and FFT(g, (G+1)). Let  $D = s_D + \langle \delta_1, \ldots, \delta_{m-1} \rangle$  where,

$$\delta_i = \gamma_i^2 - \gamma_i, \quad 1 \le i \le m - 1$$

We know that each  $\gamma_i$  is not 1 or 0, so  $\delta_i$  is not 0. Since  $\gamma_1, ..., \gamma_m$  and 1 are linearly independent over GF(2) the elements  $\delta_1, ..., \delta_{m-1}$  are linearly independent over GF(2) as well and span the affine subspace,

$$D = s_D + \langle \delta_1, \dots, \delta_{m-1} \rangle$$

of size  $k = 2^{m-1} = n/2$ .

Notation 1. Given  $\alpha = a_1 \gamma_1 + \cdots + a_{m-1} \gamma_{m-1} \in G$ , the element  $\alpha^*$  is

$$\alpha^* = \alpha^2 - \alpha = a_1 \delta_1 + \dots + a_{m-1} \delta_{m-1}$$

Therefore,

$$G[i]^* = D[i], \quad 0 \le i < k$$

Suppose we are given the Taylor expansion of g(x) at  $x^2 - x$ .

$$g(x) = \sum_{i=0}^{k-1} \left(g_{i0} + g_{i1}x\right) \cdot \left(x^2 - x\right)^i$$

(3.3)

and  $g_{ij} \in \mathbb{F}$ . Let

$$g_0(x) = \sum_{i=0}^{k-1} g_{i0} \cdot x^i$$

, and  $g_1(x) = \sum_{i=0}^{k-1} g_{i1} \cdot x^i$ . (3.4)

Notice that for any  $\alpha \in G$  and  $b \in GF(2)$ , since  $(\alpha + b)^2 - (\alpha + b) = \alpha^*$ , we have

$$g(\alpha + b) = (g_0(\alpha^*) + \alpha \cdot g_1(\alpha^*)) + bg_1(\alpha^*)$$

(3.5)

Therefore, the FFT of g(x) can be calculated from the FFTs of  $g_0(x)$  and  $g_1(x)$  over D. Let the FFT of  $g_0(x)$  and  $g_1(x)$  over D be,

$$FFT(g_0, m-1, D) = (u_0, u_1, \dots, u_{k-1}), \quad u_i = g_0(D[i])$$

$$FFT(g_1, m-1, D) = (v_0, v_1, \dots, v_{k-1}), \quad v_i = g_1(D[i])$$

(3.6)

Equation 3.5 implies that

$$FFT(g, m-1, G) = (w_0, w_1, \dots, w_{k-1})$$

Where  $w_i = u_i + G[i] \cdot u_i$  for  $0 \le i < k$ . It also implies that,

$$FFT(g, m-1, G+1) = FFT(g, m-1, G) + FFT(g_1, m-1, D).$$

This reduction step is applied recursively until the input polynomials are linear functions that can be evaluated easily. In algorithm 3.5 a summary of the written above can be found.

The only two additions we made to Gao and Mateer's algorithm is calculating recursively a series of affine shifts. The only place which these shifts take place is the bottom of the recursion, where we evaluate the linear function as described in step 1.

We will now compute the runtime of the algorithm. To compute the basis elements of G and D and the affine shifts in step 5, we perform  $2m+2(m-1)+\cdots+2\cdot 2 = m(m+1) = O(\log_2^2(n))$  multiplications, and the number of additions is  $m+(m-1)+\cdots+2 = m(m-1)/2 = O(\log_2^2(n))$ . In step 2, we compute the powers of  $\beta_m^i$  for  $2 \le i \le n-1$ , with a total number of multiplications that is at most  $(2^m-2)+(2^{m-1}-2)+\cdots+(2^2-2) < 2\cdot 2^m = 2n$ . Up until now, the whole computation can be preprocessed, and costs negligible time.

In step 1 the recursion ends and it costs 2 multiplications and 2 additions. Step 2 costs an additional n-1 multiplications (besides computing the powers of  $\beta_m$ ). The Taylor expansions cost additional  $\frac{1}{2} \cdot n \cdot \log_2(n) - \frac{1}{2} \cdot n$  additions. Step 7 has two invocations of the FFT algorithm of size n/2. Step 10 costs n multiplications and n additions. Let M(n) and A(n) denote the number of multiplications and additions performed by the algorithm, respectively, on an input of size n. Then M(2) = A(2) = 2,

| <b>Algorithm 3.5</b> Additive FFT of length $n = 2^m$                                                                                          |                                           |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|--|--|--|--|--|

| Input:                                                                                                                                         |                                           |  |  |  |  |  |

| • $f(x) \in \operatorname{GF}(2^t)[X]$ of degree $< n = 2^m$ .                                                                                 |                                           |  |  |  |  |  |

| • $B = \langle \beta_1,, \beta_m \rangle$ , a basis with linearly independent elements over GF(2).                                             |                                           |  |  |  |  |  |

| • S, an affine shift to the subspace spanned by $\beta_i$ 's.                                                                                  |                                           |  |  |  |  |  |

| <b>Output:</b> $FFT(f, m, B, S) = (f(B[0] + S),, f(B[n-1] + S))$                                                                               |                                           |  |  |  |  |  |

| 1: If $m = 1$ then return $f(S), f(S + \beta_1)$ . $\triangleright$ Linea                                                                      | ar Evaluation Phase.                      |  |  |  |  |  |

| 2: Compute $g(x) = f(\beta_m x)$ .                                                                                                             | $\triangleright$ Shift Phase.             |  |  |  |  |  |

| 3: Compute the Taylor expansion of $g(x)$ as in algorithm 3.4                                                                                  | $\triangleright$ Taylor Expansion         |  |  |  |  |  |

| Phase.                                                                                                                                         |                                           |  |  |  |  |  |

| 4: Let $g_0(x)$ and $g_1(x)$ from $g(x)$ as in (3.4).                                                                                          | $\triangleright$ Shuffle Phase.           |  |  |  |  |  |

| 5: Compute $\gamma_i \leftarrow \beta_i \cdot \beta_m^{-1}$ , $\delta_i \leftarrow \gamma_i^2 - \gamma_i$ for $1 \le i < m$ ,                  | $s_G \leftarrow S \cdot \beta_m^{-1}$ and |  |  |  |  |  |

| $s_D \leftarrow s_G^2 - s_G.$                                                                                                                  |                                           |  |  |  |  |  |

| 6: Let $G \leftarrow s_G + \langle \gamma_1, \dots, \gamma_{m-1} \rangle$ , and $D \leftarrow \langle \delta_1, \dots, \delta_{m-1} \rangle$ . |                                           |  |  |  |  |  |

| 7: Let $k = 2^{m-1}$ compute                                                                                                                   |                                           |  |  |  |  |  |

| $FFT(g_0, m-1, D, s_D) = (u_0, u_1, \dots, u_{k-1}), and$                                                                                      |                                           |  |  |  |  |  |

| $FFT(g_1, m-1, D, s_D) = (v_0, v_1, \dots, v_{k-1}).$                                                                                          |                                           |  |  |  |  |  |

| 8: for $0 \leq i < k$ do                                                                                                                       |                                           |  |  |  |  |  |

| 9: $w_i \leftarrow u_i + G[i] \cdot v_i$                                                                                                       |                                           |  |  |  |  |  |

| 10: $w_{k+1} \leftarrow w_i + v_i$ .                                                                                                           | $\triangleright$ Merge Phase.             |  |  |  |  |  |

| 11: return $(w_0, w_1, \dots, w_{n-1})$                                                                                                        |                                           |  |  |  |  |  |

and for any  $n = 2^m > 2$ , it holds that

$$M(n) = 2 \cdot M\left(\frac{n}{2}\right) + 2n - 1,$$

$$A(n) = 2 \cdot A\left(\frac{n}{2}\right) + \frac{1}{2} \cdot n \cdot \log_2(n) + \frac{1}{2} \cdot n.$$

By induction we get

$$M(n) = 2 \cdot n \cdot \log_2(n) - \frac{3n}{2} + 1, A(n) = \frac{1}{4} \cdot n \cdot (\log_2(n))^2 + \frac{3}{4} \cdot n \cdot \log_2(n)$$

# $\mathbf{CPU}$

In this chapter we briefly discuss the implementation of the additive FFT in binary fields algorithm and the finite field multiplication operation on which it relies. We rather state the functionality of our implementation so it can be compared to the GPU finite field arithmetics and implementation. We clarify that the main scope of this work is not a CPU implementation of neither additive FFTs over binary fields or these fields' multiplication and this chapter is given for completeness.

### 4.1 Finite Field Arithmetics

In this section we discuss the implementation of finite field arithmetics needed to compute the additive FFT in  $GF(2^{64})$ .

### 4.1.1 Element Representation on CPU

A GF( $2^{64}$ ) field element represented in the standard basis is a binary polynomial whose degree is at most 63. All operations are performed modulo an irreducible polynomial of degree 64, that will be denoted by r(x) Each element in GF( $2^{64}$ ) is known to be equivalent to a unique polynomial modulo r(x). Each element e will be represented in the polynomial basis using the polynomial

$$p_e(x) = \sum_{i=0}^{63} c_e^i x^i$$

### 4.1.2 Finite Field Library API

To support the implementation of the FFT algorithm on CPU we have implemented the following operations for elements in  $GF(2^{64})$ ,

Addition Given two elements a, b the representation of a + b is  $c_a \oplus c_b$ . The implementation of addition in  $GF(2^k)$  is just bitwise XOR of the two elements.

**Multiplication** See section 3.1 for a full theoretical description of this operation. Implementation is given in section 4.1.3.

Squaring Implemented as a multiplication of an element by itself.

**Exponentiation** Implemented using the repetitive squaring and multiplying algorithm.

**Inversion** The inverse of an element a is an element b s.t. there exists a polynomial q(x) for which  $a(x) \cdot b(x) + q(x) \cdot r(x) = 1$ . The inversion is implemented by implementing the extended euclidean algorithm to find this b. The inversion operation is used only n times when evaluating an FFT of a subspace of size  $2^n$  and due to the very limited use of this operation, it was implemented in a very naive manner.

### 4.1.3 Implementation of multiplication in $GF(2^{64})$

$GF(2^n)$  multiplication has received considerable attention (cf. [J. 86, E. 96]) and is implemented efficiently for CPU in popular software libraries like NTL [V. 03] and MPFQ <sup>1</sup>. Moreover, in large part because of the importance of GF ( $2^n$ ) multiplication, Intel introduced in 2010 a dedicated CPU instruction called CLMUL which performs GF (2) [x] ring multiplication of polynomials of degree up to 64 in 7–14 cycles [Fog16].

Both NTL and MPFQ use this dedicated instruction. This instruction can be used to multiply polynomials of higher-degree, thereby supporting  $GF(2^n)$  multiplication for values n > 64 (cf. [C. 12] for one such implementation).

Algorithm 6.1 shows how to perform finite field multiplication in binary fields with elements being represented in the standard basis and the irreducible polynomial is 2-Gapped. The multiplication in  $GF(2^n)$  by this algorithm is composed of three multiplications of polynomials in the ring GF(2)[X] of degrees up to k-1 and to additions of such polynomials. The multiplication of such polynomials can be implemented using the CLMUL instruction that was mentioned before. The implementation is detailed in algorithm 4.2.

Notation 2. Given a polynomial  $p(x) = \sum a_k x^k$  we will denote by  $p_i^j(x) = \sum_{k=i}^j a_k x^{k-i}$

Note that the multiplication by  $x^{32}$  in line 2 will be implemented by an arithmetic shift-left of the bits.

The NTL library proposed the same implementation shown here when performing multiplication with a 2-Gapped irreducibles in binary fields. While NTL's implementation is more general, we focused in our CPU implementation on the specific field of  $GF(2^{64})$ . The implementation, using CLMUL instruction is described in algorithm 4.2.

Our C++ implementation of algorithm 4.2 cuts NTL's implementation by half. A full comparison and performance analysis is detailed in chapter 8

<sup>&</sup>lt;sup>1</sup>http://mpfq.gforge.inria.fr/doc/doc.html

•  $r(x) = x^n + r_1(x)$ , 2-Gapped polynomial in  $\mathbb{F}_2[X]$  of degree n. Output:  $h(x) = (a(x) \odot b(x)) \mod r(x)$ 1:  $h(x) \leftarrow a(x) \odot b(x)$ 2:  $h(x) \leftarrow h_0^{3n/2-1}(x) \oplus h_{3n/2}^{2n-1}(x) \odot r_1(x) \odot x^{n/2}$ 3:  $h(x) \leftarrow h_0^{n-1}(x) \oplus h_n^{3n/2}(x) \odot r_1(x)$ 4: return h(x)

**Algorithm 4.2** 2-Gapped Multiplication in  $GF(2^{64})$  using CLMUL

### Input:

- a(x), b(x) of degree at most 63 in  $\mathbb{F}_2[X]$ .

- $r(x) = x^{64} + r_1(x)$ , 2-Gapped polynomial in  $\mathbb{F}_2[X]$  of degree 64.

**Output:**  $h(x) = (a(x) \cdot b(x)) \mod r(x)$ 1:  $h(x) \leftarrow \text{CLMUL}(a(x), b(x))$ 2:  $h(x) \leftarrow h_0^{95}(x) + \text{CLMUL}(h_{96}^{127}(x), r_1(x)) \cdot x^{32}$ 3:  $h(x) \leftarrow h_0^{63}(x) + \text{CLMUL}(h_{64}^{95}(x), r_1(x))$ 4: return h(x)

### 4.2 Parallel FFT and inverse FFT implementation

We implemented the additive FFT and IFFT algorithms of Gao and Matteer [S. 10]. The implementation was parallelized to a large number of cores using openMP [B. 07]. Unfortunately, despite being very fast for a single thread, the implementation didn't scale-up for large number of cores. The reason for this lack of scalability of this implementation is left out of the scope of this work.

# © Technion - Israel Institute of Technology, Elyachar Central Library

## Chapter 5

# GPU - Introduction of Register Cache

### 5.1 Introduction of GPUs<sup>1</sup>

The Graphics Processing Unit (GPU) is a prarallel machine that runs many threads in parallel. Threads are the basic units of execution in it that process words of size  $\mathcal{B}$ . Each thread has local memory in the form of registers. The number of registers in the GPU is limited and they are partitioned evenly among running threads. Threads are grouped into warps. A warp is a set of  $\mathcal{W}$  threads that operates in lock, i.e., at a given step all threads in the warp execute the same instruction. A thread-block is a set of warps that can share a dedicated memory used for for communication between threads of the same thread block. The set of instructions is fixed and called PTX-ISA. A set of thread-blocks is called a grid and is the largest unit of computation we are interested in, representing all running threads. It has global memory of practically unlimited size but accessing it is slower than accessing the shared memory or local memory (registers). Each thread also has a unique thread-ID which it has access to. These IDs are distributed among threads in a way that all threads of the same warp posses  $\mathcal{W}$  consecutive IDs.

Grouping threads into warps has a major significance not only on the computational model itself but on global memory accesses efficiency as well. Global memory accesses are issued by the device in the form of *transactions* where each transaction reads from or writes to a large number of addresses in a single burst. All load and store operations issued by threads of the same warp are coalesced by the device to minimize the number of transactions required to perform the requested operations. The more scattered the load/store addresses are, the more transactions will be needed to perform the load/store operation, therefore each GPU programmer must make an effort to make his global

<sup>&</sup>lt;sup>1</sup>Based on nVidia's white papers of the Fermi and Kepler architectures.

<sup>(</sup>http://www.nvidia.com/content/pdf/fermi\_white\_papers/nvidia\_fermi\_compute\_architecture\_whitepaper.pdf) (http://www.nvidia.com/content/PDF/kepler/NVIDIA-Kepler-GK110-Architecture-Whitepaper.pdf)